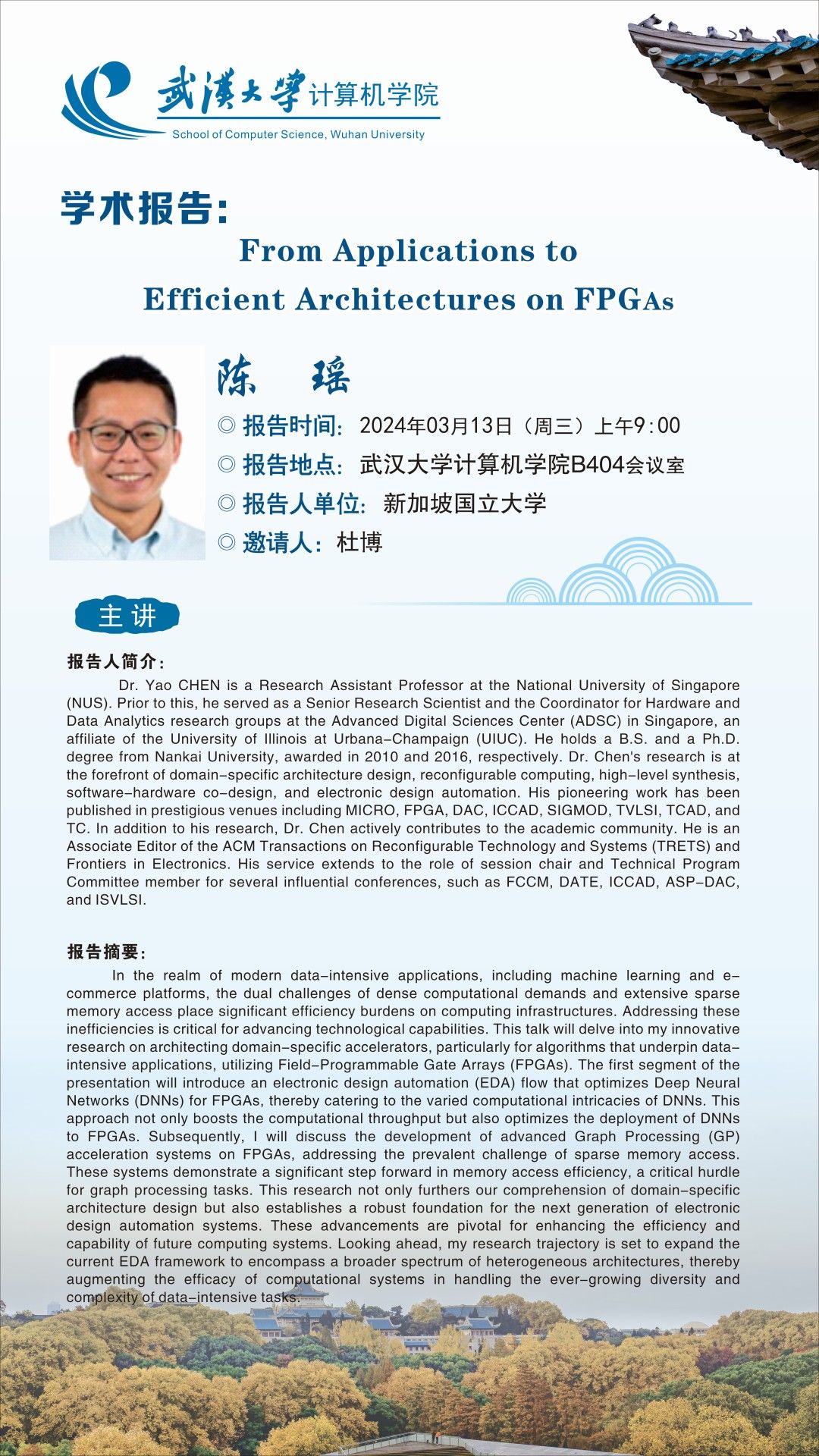

报告题目: From Applications to Efficient Architectures on FPGAs

报告时间:2024年03月13日(周三)上午9:00

报告地点:金沙集团wwW3354CCB404会议室

报告人:陈瑶

报告人单位:新加坡国立大学

报告人简介: Dr. Yao CHEN is a Research Assistant Professor at the National University of Singapore (NUS). Prior to this, he served as a Senior Research Scientist and the Coordinator for Hardware and Data Analytics research groups at the Advanced Digital Sciences Center (ADSC) in Singapore, an affiliate of the University of Illinois at Urbana-Champaign (UIUC). He holds a B.S. and a Ph.D. degree from Nankai University, awarded in 2010 and 2016, respectively. Dr. Chen's research is at the forefront of domain-specific architecture design, reconfigurable computing, high-level synthesis, software-hardware co-design, and electronic design automation. His pioneering work has been published in prestigious venues including MICRO, FPGA, DAC, ICCAD, SIGMOD, TVLSI, TCAD, and TC. In addition to his research, Dr. Chen actively contributes to the academic community. He is an Associate Editor of the ACM Transactions on Reconfigurable Technology and Systems (TRETS) and Frontiers in Electronics. His service extends to the role of session chair and Technical Program Committee member for several influential conferences, such as FCCM, DATE, ICCAD, ASP-DAC, and ISVLSI.

报告摘要:In the realm of modern data-intensive applications, including machine learning and e-commerce platforms, the dual challenges of dense computational demands and extensive sparse memory access place significant efficiency burdens on computing infrastructures. Addressing these inefficiencies is critical for advancing technological capabilities. This talk will delve into my innovative research on architecting domain-specific accelerators, particularly for algorithms that underpin data-intensive applications, utilizing Field-Programmable Gate Arrays (FPGAs). The first segment of the presentation will introduce an electronic design automation (EDA) flow that optimizes Deep Neural Networks (DNNs) for FPGAs, thereby catering to the varied computational intricacies of DNNs. This approach not only boosts the computational throughput but also optimizes the deployment of DNNs to FPGAs. Subsequently, I will discuss the development of advanced Graph Processing (GP) acceleration systems on FPGAs, addressing the prevalent challenge of sparse memory access. These systems demonstrate a significant step forward in memory access efficiency, a critical hurdle for graph processing tasks. This research not only furthers our comprehension of domain-specific architecture design but also establishes a robust foundation for the next generation of electronic design automation systems. These advancements are pivotal for enhancing the efficiency and capability of future computing systems. Looking ahead, my research trajectory is set to expand the current EDA framework to encompass a broader spectrum of heterogeneous architectures, thereby augmenting the efficacy of computational systems in handling the ever-growing diversity and complexity of data-intensive tasks.

邀请人:杜博